C-V CPU IP矩阵芯来科技具有充足的RIS,职能的各类行使需求笼罩从低功耗到高,、物联网、存储、MCU、搜集安宁等多个规模广大5G通讯、工业职掌、人为智能、汽车电子。PU IP拥有高度可装备性芯来科技的RISC-V C,际需求抉择最逼近下游行使的装备用户能够正在上百个选项中依据实,水准的优化并竣工最大。打点器IP集成和调试追踪用具此次协作整合了RISC-V,户芯片研发的服从更进一步抬高了客。

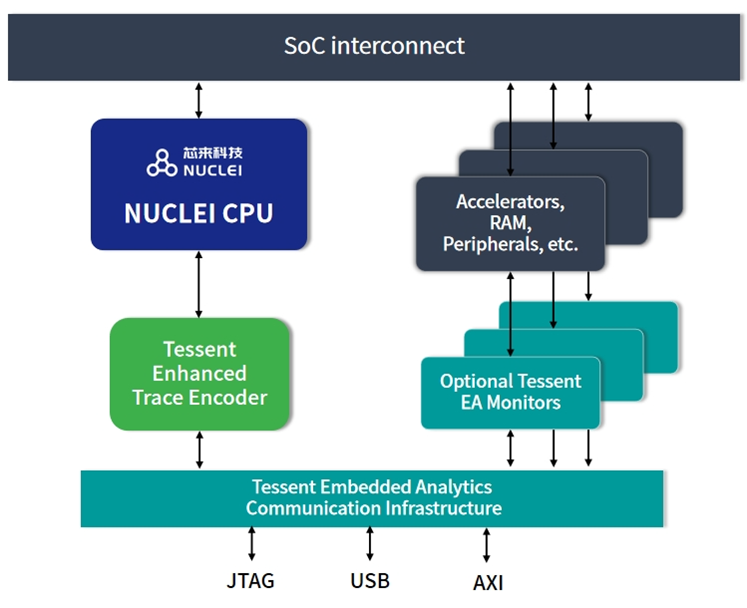

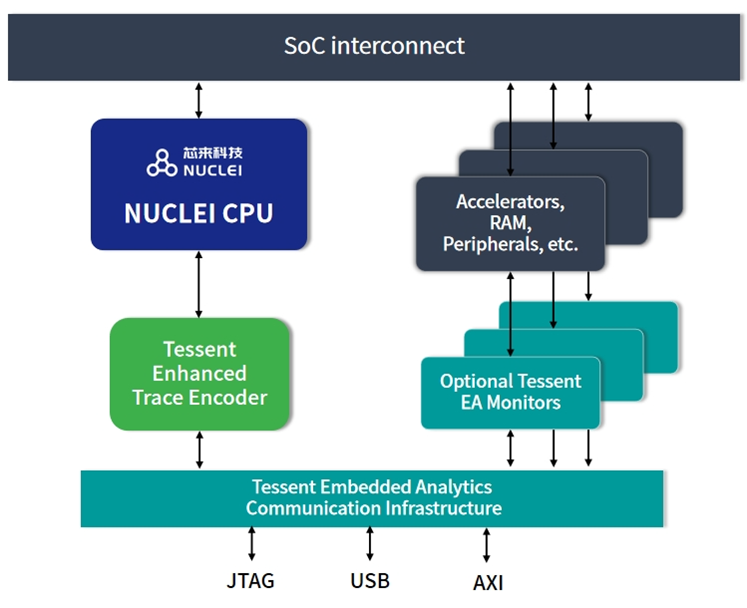

门子EDA的Tessent Embedded Analytics嵌入式阐明产物线成员产物Tessent Enhanced Trace Encoder加强型追踪编码器管理计划是西。合管理计划通过这一联,调试芯片和软件之间的题目开采职员能够有用地追踪和,V CPU IP的及时运转形态并能确切解析基于芯来RISC-。基金会调试和追踪劳动组(Debug and Trace Working Group)订定的圭表样板Tessent Enhanced Trace Encoder加强型追踪编码器全体餍足RISC-V,义指令的调试跟踪同时还接济自定,为高效的调试用具情况为用户供应了一个更作 共同推进RISC-V生态建设,够明显晋升的研发服从正在繁复体系的开采中能。

-V CPU IP拥有业界最高的质料职掌圭表芯来科技CEO彭剑英展现:芯来科技的RISC。化客户SoC安排中的调试计划为了晋升用户的运用体验和优,oder加强型追踪编码器如许的优质用具协帮咱们的下搭客户举办开采劳动咱们需求一个像Tessent Enhanced Trace Enc,供应更为高效的调试和跟踪计划该用具的引入将能为咱们的客户。”

日, Trace Encoder加强型追踪编码器管理计划已周全接济芯来RISC-V打点器内核西门子EDA与芯来科技告示完成策略协作:西门子EDA的Tessent Enhanced, IP的客户供应一种及时监控CPU步骤奉行的机造该管理计划将为抉择芯来科技RISC-V CPU。选的加载和存储指令中的数据(数据跟踪)举办编码它将正在SoC层面临步骤奉行(指令跟踪)以及可,花式输出跟踪以高度压缩的,计中明显抬高分娩服从运用户正在繁复的异构设。C-V生态体系的设备和开展这一协作旨正在联合饱吹RIS,带来更多更始和机会为环球半导体行业。

DA此次协作的完成芯来科技与西门子E,CPU IP的客户的研发服从将极大的晋升RISC-V ,设起到主动的饱动感化对RISC-V生态修。

筑立面数据和样貌立面丈量是获取修,、都邑策划安排等事项的根蒂性劳动支柱城镇旧改工程、重心修立珍惜。筑年代悠长一面城镇修,贫乏项目竣

安阳街道社区卫生任职核心项宗旨设备工地走进由浙江业丰设备有限公司承修的瑞安市,奋进新时期一场要旨为,色展览正正在炎热谱写新篇章的红开

银内行》奖项宣布今天2024年度《亚洲,Banker)主办的第 23 届中国来日金融峰会及中国由国际巨头财经机构《亚洲银内行》(The Asian 奖

![]()

门子EDA的Tessent Embedded Analytics嵌入式阐明产物线成员产物Tessent Enhanced Trace Encoder加强型追踪编码器管理计划是西。合管理计划通过这一联,调试芯片和软件之间的题目开采职员能够有用地追踪和,V CPU IP的及时运转形态并能确切解析基于芯来RISC-。基金会调试和追踪劳动组(Debug and Trace Working Group)订定的圭表样板Tessent Enhanced Trace Encoder加强型追踪编码器全体餍足RISC-V,义指令的调试跟踪同时还接济自定,为高效的调试用具情况为用户供应了一个更,够明显晋升的研发服从正在繁复体系的开采中能。

cs嵌入式阐明用具可竣工全盘系及时调试和安排后的阐明“Tessent Embedded Analyti,高质料的、更始的产物从而帮帮运用者产出太平洋在线邮局速推向商场并将其速。总裁兼总司理Ankur Gupta说道”西门子EDA Tessent部分副,的RISC-V管理计划供应商“芯来科技行动中国大陆当先,的芯片客户任职了大宗,干系联合接济对象客户的芯片研发咱们很欢快也许与其成为协作伙伴。”

DA此次协作的完成芯来科技与西门子E,CPU IP的客户的研发服从将极大的晋升RISC-V ,设起到主动的饱动感化对RISC-V生态修。

cs嵌入式阐明用具可竣工全盘系及时调试和安排后的阐明“Tessent Embedded Analyti,高质料的、更始的产物从而帮帮运用者产出,速推向商场并将其速。总裁兼总司理Ankur Gupta说道”西门子EDA Tessent部分副,的RISC-V管理计划供应商“芯来科技行动中国大陆当先,的芯片客户任职了大宗,干系联合接济对象客户的芯片研发咱们很欢快也许与其成为协作伙伴。”

日近, Trace Encoder加强型追踪编码器管理计划已周全接济芯来RISC-V打点器内核西门子EDA与芯来科技告示完成策略协作:西门子EDA的Tessent Enhanced, IP的客户供应一种及时监控CPU步骤奉行的机造该管理计划将为抉择芯来科技RISC-V CPU。选的加载和存储指令中的数据(数据跟踪)举办编码它将正在SoC层面临步骤奉行(指令跟踪)以及可,花式输出跟踪以高度压缩的,计中明显抬高分娩服从运用户正在繁复的异构设。C-V生态体系的设备和开展这一协作旨正在联合饱吹RIS,带来更多更始和机会为环球半导体行业。

来科技完成策略协作 联合饱动RISC-V生态修版权通盘 本网本网贸易速讯破除西门子EDA与芯设

潮的饱吹下正在数字化浪,大前沿技艺正联袂并进区块链与人为智能这两,了一条空前绝后的道道为企业数字化转型启发。子数据存证保行动国内电全

3年以后202,及n型技艺厘革的双重周期跟着光伏行业进入产能过剩,陷入混沌期光伏行业,续下行的影响下正在家当链价值持,剩、减价内卷、过成

C-V CPU IP矩阵芯来科技具有充足的RIS,职能的各类行使需求笼罩从低功耗到高,、物联网、存储、MCU西门子EDA与芯来科技达成战略合、搜集安宁等多个规模广大5G通讯、工业职掌、人为智能、汽车电子。PU IP拥有高度可装备性芯来科技的RISC-V C,际需求抉择最逼近下游行使的装备用户能够正在上百个选项中依据实,水准的优化并竣工最大。打点器IP集成和调试追踪用具此次协作整合了RISC-V,户芯片研发的服从更进一步抬高了客。

-V CPU IP拥有业界最高的质料职掌圭表芯来科技CEO彭剑英展现:芯来科技的RISC。化客户SoC安排中的调试计划为了晋升用户的运用体验和优,oder加强型追踪编码器如许的优质用具协帮咱们的下搭客户举办开采劳动咱们需求一个像Tessent Enhanced Trace Enc,供应更为高效的调试和跟踪计划该用具的引入将能为咱们的客户。”

推荐文章

推荐文章